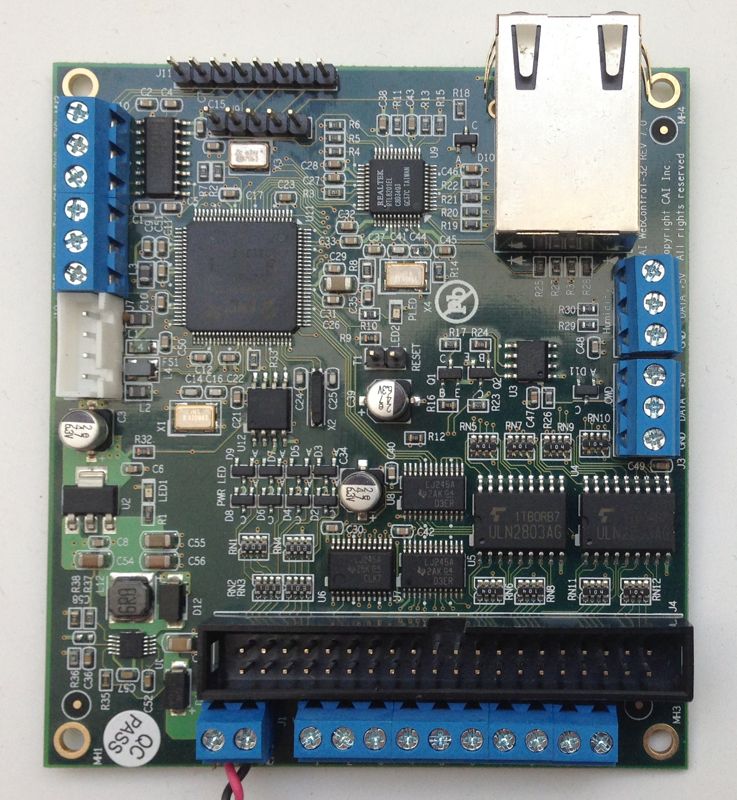

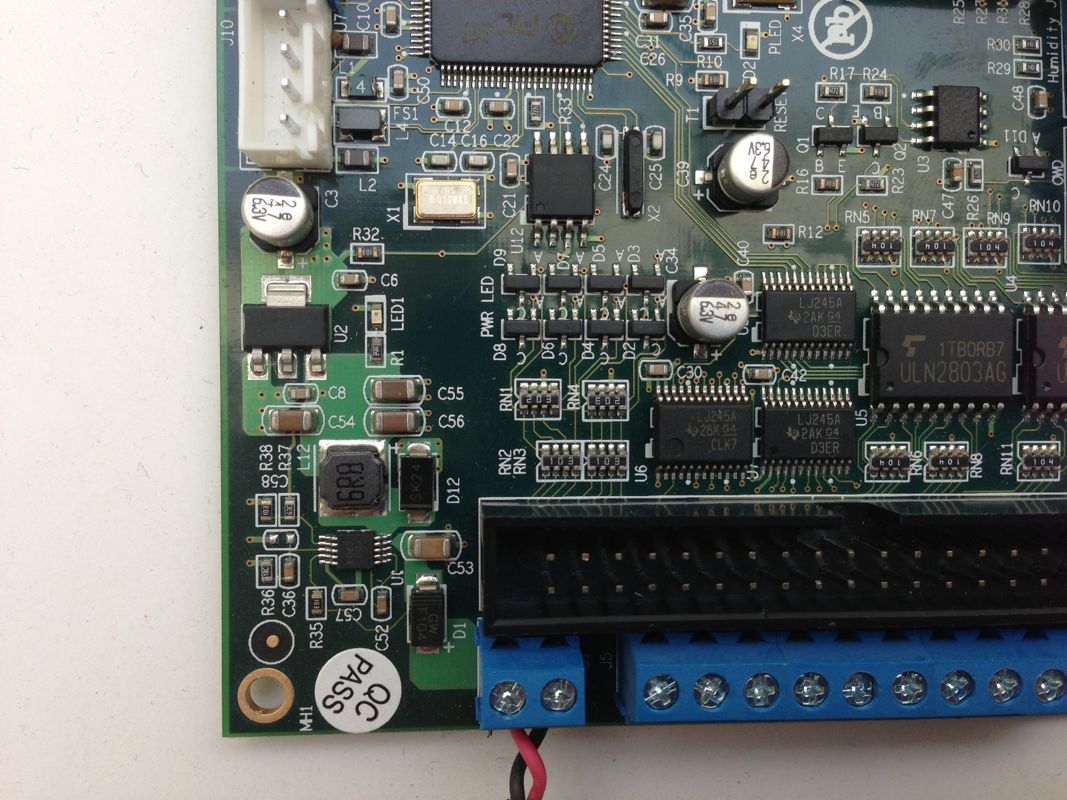

Yes it appears the same as your board. it seems the switcher is quite tiny. And the vendor verified that despite the +9v labeling it is good to go for the full range. thanks for the confirmation and the pictures

rossw said:

Sounds like you've got its address wrong. Returning all FF means it's not replying on the bus.

Yeah I had that thought, and even tried putting all four of them on the bus, each wired so that all four addresses were there, and tested each. some simple code or byte logic thing that I haven't learned yet, or have forgotten thru disuse

As far as the address, both cai support and the datasheet say that grounding the addr pin will make it 0x48, and that's where I started. hex 48 is 1001000, adding the low zer0 bit for the write makes it 10010000 = 0x90

i2cwrite 1 0 0x90 # 10010000 address

i2cwrite 0 0 0x1 # 00000001 pointer to config register

the first half of the first config byte sets the input, 100 for aip0 single ended, so 1100

the second half is the pga, I tried various values, but 000 for +/- 6.144v seemed like it should be fine for a max 5v input

the last bit is the continuous or single shot mode, I tried both. single is a 1, so 0001

gluing those together makes 11000001 = 0xc1 for aip0, singleread, pga = +/- 6.144v. so next line is

i2cwrite 0 0 0xc1

selecting other pga or mode options might make this 0xc2, 0xc3, or 0xc4, etc

selecting one of the other inputs would make this variously 0xd1, 0xe1, or 0xf1, etc

the second config byte in their example, and the defaults, with comparator disabled, is 10000011 = 0x83

i2cwrite 0 1 0x83

config set. next set pointer to conversion register:

i2cwrite 1 0 0x90 # address 0x48 plus write 0 bit appended

i2cwrite 0 0 0x0 # points to Conversion register

next come the reads:

i2cwrite 0 0 0x91 # address 0x48 plus read 1 bit appended

i2cread 0 0 RAM21 # store MSB aip0 conversion value in MSB RAM2L

i2cread 1 1 RAM20 # store LSB aip0 conversion value in LSB RAM2L

put it where it can be seen:

SET VAR2 RAM2L # 65535

the default data rate is 128 SPS, about 8ms, I don't know how the wc handles these timings. I tried some various delays for the read, based on the BMP180 example, but no help